| Nombre de processeur | i5-520M |

| Famille | Mobile du noyau i5 |

| Technologie (micron) | 0,032 |

| Vitesse du processeur (gigahertz) | 2,4 |

| Taille de la cachette L2 (KB) | 512 |

| Taille de la cachette L3 (mb) | 3 |

| Le nombre de noyaux | 2 |

| EM64T | Soutenu |

| Technologie de HyperThreading | Soutenu |

| Technologie de virtualisation | Soutenu |

| Technologie augmentée de SpeedStep | Soutenu |

| Caractéristique de peu d'Exécuter-débronchement | Soutenu |

Informations générales :

|

| Type | Unité centrale de traitement/microprocesseur |

| Segment de marché | Mobile |

| Famille | Mobile d'Intel Core i5 |

| Numéro de type | i5-520M |

| Fréquence | 2400 mégahertz |

| Fréquence maximum de turbo | 2933 mégahertz (1 noyau)

2667 mégahertz (2 noyaux) |

| Fréquence de puissance faible | 1200 mégahertz |

| Vitesse d'autobus | 2,5 GT/s DMI |

| Multiplicateur d'horloge | 18 |

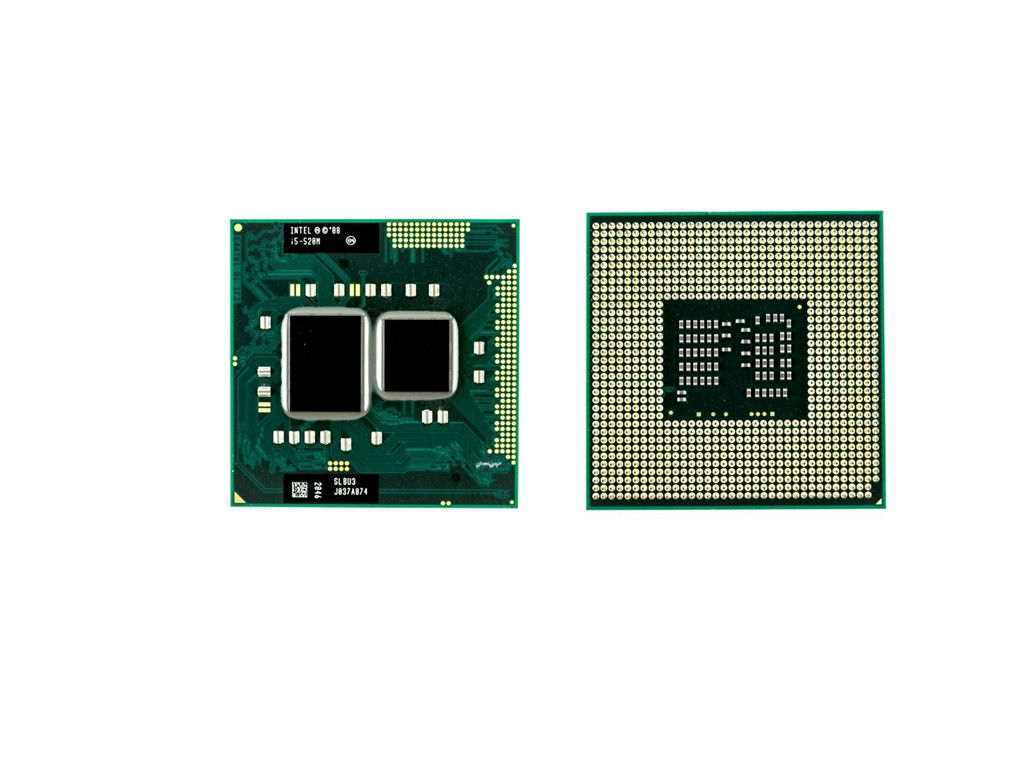

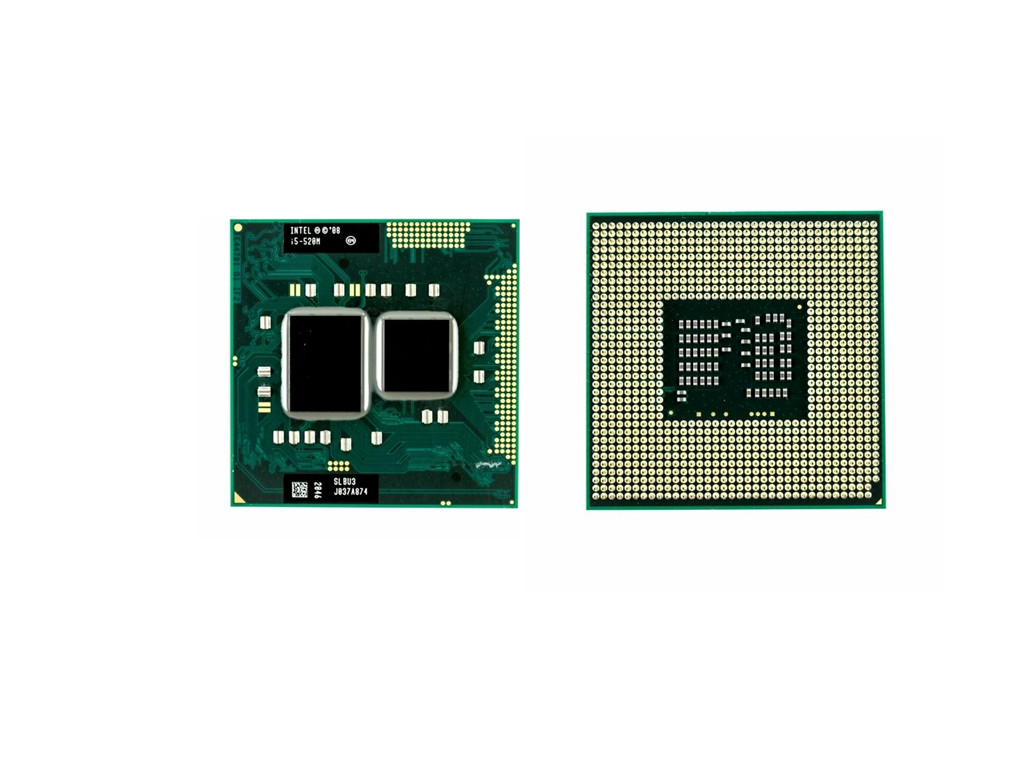

| Paquet | 988-pin micro-FCPGA (rPGA988A) |

| Prise | Prise G1/rPGA988A |

| Taille | 1,48 » » de x 1,48/3.75cm x 3.75cm |

| Date d'introduction | 7 janvier 2010 |

| Date de la Fin-de-vie | La date passée d'ordre pour les processeurs enfermés dans une boîte est le 19 octobre 2012

La date passée d'expédition pour les processeurs enfermés dans une boîte est le 18 janvier 2013 |

| | |

Architecture/Microarchitecture :

|

| Microarchitecture | Westmere |

| Plate-forme | Calpella |

| Noyau de processeur | Arrandale |

| Steppings de noyau | C2 (Q3GB, SLBNB)

K0 (Q4CN, SLBU3) |

| CPUIDs | 20652 (Q3GB, SLBNB)

20655 (Q4CN, SLBU3) |

| Processus de fabrication | 0,032 microns

382 millions de transistors (l'unité centrale de traitement meurent)

177 millions de transistors (IMC/graphiques meurent) |

| Mourez | 81mm2 (l'unité centrale de traitement meurent)

114mm2 (IMC/graphiques meurent) |

| Largeur de données | bit 64 |

| Le nombre de noyaux d'unité centrale de traitement | 2 |

| Le nombre de fils | 4 |

| Unité de virgule flottante | Intégré |

| Taille de cachette de niveau 1 | cachettes associatives réglées d'instruction de manière de 2 x 32 KBs 4

cachettes associatives réglées de données de manière de 2 x 32 KBs 8 |

| Taille de cachette de niveau 2 | cachettes associatives réglées de manière de 2 x 256 KBs 8 |

| Taille de cachette du niveau 3 | 3 cachette partagée associative réglée de manière du mb 12 |

| Mémoire physique | 8 GIGAOCTETS |

| Multitraitement | Non soutenu |

| Caractéristiques | Instructions du § MMX

§ SSE/couler des prolongements de SIMD

§ SSE2/couler les prolongements 2 de SIMD

§ SSE3/couler les prolongements 3 de SIMD

§ SSSE3/prolongements coulants supplémentaires 3 de SIMD

§ SSE4/SSE4.1 + SSE4.2/couler les prolongements 4 de SIMD

Le § AES/a avancé des instructions de norme de chiffrage

§ EM64T/technologie mémoire prolongée 64/Intel 64

HT de §/technologie de Hyper-filetage

§ TBT/technologie de Turbo Boost

Le § NX/XD/exécutent le peu de débronchement

Technologie de VT-x/virtualisation de §

VT-d de §/virtualisation pour l'entrée-sortie dirigée

Le § TXT/a fait confiance à la technologie d'exécution |

| Caractéristiques de puissance faible | États C1, C3 et C6 de fil de §

États C1/C1E, C3 et C6 de noyau de §

États C1/C1E, C3 et C6 de paquet de §

Le § a augmenté la technologie de SpeedStep |

Périphériques/composants intégrés :

|

| Graphiques intégrés | Type de GPU : HD (Westmere)

Fréquence basse (mégahertz) : 500

Fréquence maximum (mégahertz) : 766

Le nombre d'affichages soutenus : 2 |

| Contrôleur de mémoire | Le nombre de contrôleurs : 1

Canaux de mémoire : 2

Largeur de la Manche (peu) : 64

Mémoire soutenue : DDR3-800, DDR3-1066

Largeur de bande maximum de mémoire (GB/s) : 17,1

CCE soutenue : Non |

| D'autres périphériques | Interface directe de médias de §

Interface de PCI Express 2,0 de § |

Paramètres électriques/thermiques :

|

| Noyau V | 0.8V - 1.4V (mode à haute fréquence)

0.775V - 1V (mode basse fréquence) |

| Température de fonctionnement minimum/maximum | 0°C - 105°C |

| Dissipation de puissance maximum | 3,8 watt (TDP dans) d'état C6/67,2 watts (crête, noyau d'unité centrale de traitement seulement)

44,8 watts (soutenus, noyau d'unité centrale de traitement seulement) |

| Thermal Design Power | 35 watts (paquet)

25 watts (noyau d'unité centrale de traitement)

12,5 watts (noyau de graphiques) |

Votre message doit contenir entre 20 et 3 000 caractères!

Votre message doit contenir entre 20 et 3 000 caractères! Merci de consulter vos emails!

Merci de consulter vos emails!  Votre message doit contenir entre 20 et 3 000 caractères!

Votre message doit contenir entre 20 et 3 000 caractères! Merci de consulter vos emails!

Merci de consulter vos emails!